| Mentor Graphics TestKompress-Xpress-Technologie deckt Testanforderungen bei der Herstellung von 65/45-nm-ICs ab |

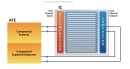

| WILSONVILLE, Oregon/USA, 01. Oktober 2007 Mentor Graphics kündigt für sein Automatic-Test-Pattern-Generation- (ATPG) Produkt TestKompress eine neue Technologie an, die den wachsenden Bedarf der Industrie nach Scan-Test-Kompression abdeckt. Mentors neue Xpress-Technologie bietet einen Kompressionsgrad um mehr als das 100-Fache und erlaubt es IC-Herstellern, ihre anspruchsvollsten Qualitätsziele für fortschrittliche Prozessknoten zu erreichen, ohne die Testkosten in die Höhe zu treiben. Die jüngsten Forstschritte beim Herstellungsprozess von integrierten Schaltungen haben die Anzahl der Gatter auf einem IC drastisch erhöht, weshalb auch der Umfang der Testmuster weiter zunimmt. Zudem führen schrumpfende Geometrien zu neuen Fehlermechanismen. Um die Qualität der gelieferten Produkte zu erhalten, müssen die Hersteller erweiterbare Scan-Tests wie At-speed- und Small-delay-Tests einsetzen, die komplizierte Fehler finden und den DPM (Defects per Million) Level niedrig halten. Das Hinzufügen neuer Testtypen vergrößert den Testmusterumfang um ein Vielfaches und diese Tendenz wird sich erwartungsgemäß an jedem Prozessknoten beschleunigen. Daher ist die Komprimierung der Testmuster eine entscheidende Anforderung für qualitativ hochwertige Fertigungstests. Die International Technology Roadmap for Semiconductors (ITRS) prognostiziert, dass die Industrie bis 2008 eine Kompression der Testdatenvolumen um das 200-Fache benötigen wird, wobei die Anforderung innerhalb der nächsten fünf Jahre exponentiell steigen werden. Mentors TestKompress-Produkt, das 2001 als erstes kommerzielles ATPG-Werkzeug mit Onchip-Testkompression auf den Markt kam, verfügt über eine Roadmap, um diese zukünftigen Kompressionsziele mit Innovationen wie der neuen Xpress Pattern Compaction-Technologie zu erfüllen. Die neueste Version von TestKompress erhöht den erzielbaren Kompressionsgrad, indem sie einen effizienteren Weg zur Handhabung so genannter X-States zur Verfügung stellt. X sind unbekannte Zustände, die während eines Fertigungstests auftreten können. Wenn Sie nicht richtig gehandhabt werden können X die Testabdeckung verringern und sie tendieren dazu, den für einen sorgfältigen Bausteintest erforderlichen Testmusterumfang zu vergrößern. Die innovative, patentierte Xpress Pattern Compaction-Technologie bietet einen effizienteren Weg, X zu handhaben. Sie kombiniert eine hoch entwickelte Schaltung zur Auswahl der Embedded-Testdaten mit einem fortschrittlichen Softwaresteuerungsalgorithmus. Da die Xpress-Technologie die Effekte der X effizienter maskiert, werden die Testmuster kleiner und lassen sich höher komprimieren. Höher komprimierte Testmuster führen zu kürzeren Testzeiten, höherem Durchsatz bei den Produktionstests, niedrigeren Fertigungskosten und verlängern die Betriebsdauer von bestehenden Testanlagen. Der Einsatz der Xpress-Technologie erfordert keine Änderungen im funktionalen Design und ist vollständig transparent für den TestKompress-Anwender. Deshalb gibt es auch keine zusätzliche Lernkurve. Der Kompressionsbedarf der Industrie hat nicht nachgelassen, seit wir die Kompression erstmals im Jahr 2001 in den Markt eingeführt haben. Da unsere Kunden jeden Embedded-Kompressionsgrad sehr schnell adaptieren, glauben wir vielmehr, dass die ITRS-Kompressions-Roadmap ein genaues Bild des Industriebedarfs wider spiegelt, sagte Robert Hum, Vice President und General Manager der Design Verification und Test Division von Mentor Graphics. Mentor engagiert sich für modernste Kompressionstechnologien. Damit decken wir nicht nur den derzeitigen Bedarf ab, sondern auch zukünftige Anforderungen von Deep-Submicron-IC-Test. Verfügbarkeit TestKompress Xpress ist für Beta-Evaluationen erhältlich. In Produktion wird es mit dem Vierten-Quartals-Release von TestKompress gehen, dessen Auslieferung für November 2007 geplant ist. (Mentor Graphics und TestKompress sind eingetragene Warenzeichen der Mentor Graphics Corporation. Alle übrigen Unternehmens- oder Produktnamen sind eingetragene Warenzeichen oder Warenzeichen ihrer jeweiligen Besitzer.) |

| Über Mentor Graphics Mentor Graphics Corporation (Nasdaq: MENT) gehört zu den weltweit führenden Unternehmen, die Software- und Hardwarelösungen für die Entwicklung elektronischer Schaltungen anbieten. Zu Mentors Portfolio gehören Produkte, Beratungs- und Supportdienstleistungen, auf die die weltweit erfolgreichsten Elektronik- und Halbleiterhersteller vertrauen und dies mit der Verleihung zahlreicher Auszeichnungen an Mentor zum Ausdruck gebracht haben. Das 1981 gegründete Unternehmen erzielte in den zurückliegenden zwölf Monaten einen Gesamtumsatz von über 800 Mio. US-Dollar und beschäftigt weltweit ca. 4.200 Mitarbeiter. Der Hauptsitz von Mentor Corporate befindet sich den USA, 8005 S.W. Boeckman Road, Wilsonville, Oregon 97070-7777; Die Adresse der Niederlassung im Silicon Valley lautet: 1001 Ridder Park Drive, San Jose, Kalifornien 95131-2314. Weitere Informationen unter: www.mentor.com |

| Presse Informationen online: | 5999 |

| Presse Informationen | | | Newsletter | | | Suche | | | Agentur | | | English |