# Kompression – Eine entscheidende Technologie für Produktionstest von Nanometer-ICs

Hintergrundinformation

## Überblick

Fortschritte beim Herstellungsprozess von integrierten Schaltungen haben den Effekt, dass sie sich auf die Beschaffenheit der Fehlermechanismen auswirken. Um die Qualität der gelieferten Produkte erhalten und die stetig zunehmenden Designgrößen handhaben zu können, müssen die Hersteller erweiterbare Scan-Tests einsetzen, die komplizierte Fehler finden und den DPM (Defects per Million) Level niedrig halten. Da die Testmustersätze umfangreicher werden, wird die Komprimierung der Testmuster zum entscheidenden Faktor für die Überwachung der Testkosten. Die "International Technology Roadmap for Semiconductors" (ITRS) prognostiziert, dass die Industrie bis 2008 eine Kompression der Testdatenvolumen um das 200-Fache benötigen wird. Dabei werden die Anforderungen innerhalb der nächsten fünf Jahre exponentiell steigen, um den Testqualitätsbedarf der Industrie abzudecken.<sup>1</sup>

Für Halbleiterunternehmen wird eine Technologie immer wichtiger, die einen sehr hohen Kompressionsgrad für Tests liefern kann, ohne dafür mit höherer Designkomplexität, Verringerung der Testabdeckung oder –qualität oder zusätzlicher Komplexität im Testgenerierungsprozess bestraft zu werden. Mentor Graphics verfügt über eine aggressive Roadmap zur Testkomprimierung, die innerhalb der nächsten Jahre Kompressionsfaktoren vom 1000-Fachen an aufwärts zum Ziel hat. Dies wird durch eine Kombination von mehreren Technologien erreicht, die bestehen Barrieren überwinden und Testdurchsätze sowie Kostensenkungen erzielen, die von anderen IC-Testwerkzeugen unerreichbar sind. Der Artikel beschreibt die neue Xpress-Technologie, die jüngste Innovation in Mentors TestKompress®-ATPG-Produktline. Diese patentierte Technologie erweitert den Kompressionsbereich von mit TestKompress-ATPG erzeugten Mustern auf das mehr als 100-Fache und ist für bestehende Anwender vollständig transparent.

\_

<sup>&</sup>lt;sup>1</sup> International Technology Roadmap for Semiconductors 2006 Update, Test and Test Equipment, ITRS, www.itrs.net/Links/2006Update/FinalToPost/03 Test2006Update.pdf.

#### **IC-Testtrends in der Industrie**

Da integrierte Schaltungen Millionen kleinerer Komponenten (Gatter, Vias und Leitungen) enthalten und jede möglicherweise während des Fertigungsprozesses fehlerhaft sein kann, sind sorgfältige Tests erforderlich, die alle Komponenten überprüfen. Anfangs testeten die Hersteller die Bauelemente mit Testmustern, die deren Funktion imitierten, das heißt, sie führten funktionale Tests durch. Die Komplexität der Designs machte es jedoch bald unmöglich, jedes Gatter nur mit funktionalen Tests zu überprüfen. Deshalb wechselten die Testingenieure auf strukturelle Tests in Form von Scan-Tests. Scan-Tests teilen ein komplexes sequentielles Design in eine Reihe von kleinen, leicht testbaren kombinatorischen Logikblöcken. Dies geschieht, indem sie während des Designprozesses spezielle "Scan-Chain"-Schaltkreise in den Chip integrieren. Scan-Chains schieben die Testdaten in jedes Speicherelement (Flip-Flop) im Design. Dadurch erhält der Tester Zugang zu tief im Chip vergrabenen Schaltungen. Wenn jedes der resultierenden Teile der Schaltungslogik richtig arbeitet, wird deren Kombination – das vollständige Bauelement – ebenfalls funktionieren. Mit Scan-Strukturen können Automatic-Test-Pattern-Generation (ATPG) Werkzeuge methodisch Tests generieren, die jede Komponente im Design überprüfen. Scan-Technologien und ATPG wurden zur Standardtestmethode für digitale Designs, denn sie automatisieren die Aufgabe, eine hohe Testabdeckung für hochkomplexe ICs zu erstellen.

## Änderungen beim Silizium stellen neue Anforderungen an die Tests

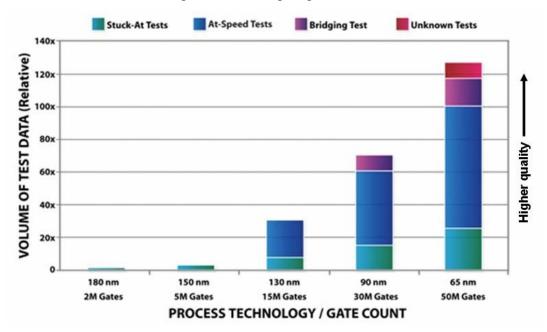

Kein IC-Hersteller möchte, dass ein defektes Bauteil seine Produktionstests verlässt und in Kundenhand gelangt. Deshalb wird der Inhalt der Produktionstests kontinuierlich angepasst, um mit den Fortschritten in der Prozesstechnologie und deren Einflüsse auf die Tests mithalten zu können. Anfänglich nutzten Scan-Tests ein Stuck-at-Fehlermodell für statische Fehler. Als sich die Herstellungsprozesse in Richtung 130 nm und darunter bewegten, traten immer mehr zeitspezifische Fehler auf. Bei diesen Technologieknoten sind nun At-speed-Tests (zusätzlich zu den Stuck-at-Tests) Standardkomponenten für die endgültigen Produktionstests. Da die Unternehmen nun auf 65 nm und darunter wech-

seln, besteht Interesse an weiteren fortschrittlichen Testmustertypen, die auf diesen kleinen Technologieknoten noch raffinierter Fehler erkennen.

Das Problem beim Hinzufügen zusätzlicher Testmustertypen bei jedem nachfolgendem Technologieknoten ist, dass dies zu einem exponentiellen Anstieg des Testdatenumfangs und der Testzeit führt. Allein At-speed-Testmuster blähen den Testmusterumfang auf das Drei- bis Fünffache der Größe von bloßen Stuck-at-Tests. Wird dies außer Acht gelassen, kann es die Testzeiten und Stückkosten erheblich beeinflussen. Mit jedem nachfolgenden Prozessknoten vergrößern steigende Gatterzahlen und zusätzliche Fehlermodelle das Problem. Zur gleichen Zeit haben mehrere Industriezweige wie die Automobil- und Medizinbranche Null-Fehlerinitiativen eingeführt. Deren Ziel ist es, die Testabdeckung auf einen Level anzuheben, bei dem kein defektes Bauelement dem Testprozess entgeht. Dies stellt jedoch noch mehr Anforderungen an den endgültigen Produktionstest.

Bild 1. Die steigende Gatteranzahl führt zusammen mit dem Hinzukommen neuer Testarten zu einer exponentiellen Zunahme des Produktionstestdatenumfangs.

Über die bereits diskutierten Stuck-at- und At-speed-Tests hinaus, tauchen neue Fehlermodelle auf, die versorgt werden müssen und die den DPM-Level erhöhen, da die Prozesstechnologien weiter schrumpfen. Layout-bezogene Tests wie Bridging-Muster nutzen die Layoutdaten des Designs, um den wahrscheinlichsten Ort zu ermitteln, an dem Signal-zu-Signal-Kurzschlüsse auftreten können. Diese Ortsangaben werden dann an die ATPG-Software weitergeleitet, die für diese Ortsangaben und Fehlermechanismen spezielle Muster erzeugt. Ebenso ergeben sich neue timing-bezogene Tests, welche die Timing-Informationen eines Designs nutzen, um das Auffinden kleiner Verzögerungsfehler zu verbessern, zum Beispiel geringfügig resistive Vias und Verbindungen. Der allgemeine Ansatz ist die Verwendung von Timing-Information, um die Tests mit minimalem Zeitversatz an die Leiterbahnen weiterzuleiten. Dies ermöglicht die Erkennung von kleineren Verzögerungsfehlern und verbessert die Qualität der Tests.

## **Der Kompressionsbedarf**

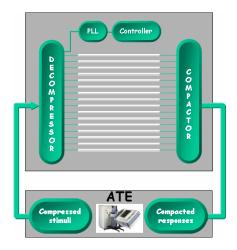

Um den sprunghaften Anstieg der Testdatenabdeckung zu managen, ist eine neue Testmethodik erforderlich, die so genannte Embedded-Kompression. Die Embedded-Kompression überwindet die Begrenzungen der physikalischen Bandbreiten, die mit dem Übertragen von Testdaten in einen und aus einem IC über eine begrenzte Anzahl von Pins verbunden sind. Kompressionstechnologien umfassen einfache Schnittstellenschaltungen zwischen dem Tester und der internen Scan-Chain des Chips. Dazu kommt ausgeklügelte Software, welche die Testmuster vor dem Abspeichern im Tester komprimiert, ähnlich wie das MP3-Verfahren Audiodateien komprimiert. Die so genannte "Decompressor-Compactor"-Schnittstellenschaltung dekomprimiert die komprimierten Testmuster innerhalb des Chips und packt (komprimiert) die resultierenden Testdaten, bevor diese zurück an den Tester gesendet werden. Auf diese Weise reduziert Testkompression den Datenumfang (aus der Perspektive des Testers) und verbessert den Testdurchsatz um Größenordnungen.

Bild 2. Embedded-Kompression überträgt über eine kleine Anzahl externer Pins eine Reihe komprimierter Testsätze.

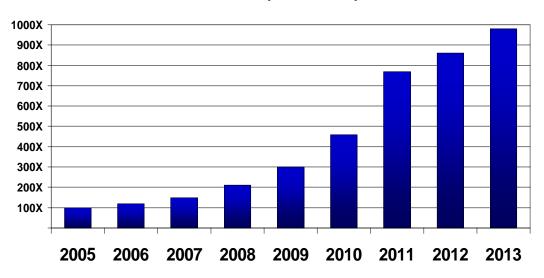

Wie viel Kompression ist erforderlich, um die Testanforderungen abzudecken, die mit jedem nachfolgenden Prozessknoten steigen? Im Jahr 2006 schätzte die "International Technology Roadmap for Semiconductors (ITRS)", dass die Produktionstests derzeit einen Kompressionsgrad von mehr als das 100-Fache benötigen. Um innerhalb der nächsten fünf Jahre mit dem Bauelementewachstum und Qualitätsanforderungen Schritt zu halten, sind Kompressionen bis zum 1000-Fachen erforderlich.

## **Test Data Volume Compression Requirements**

Bild 3. Von ITRS projizierte Anforderungen an die Testkompression.

## X-States – der Feind der Kompression

Eine der größten Herausforderungen beim Erzielen sehr hoher Kompressionsgrade ist eine effiziente Handhabung unbekannter Werte (oder X-States) während der Tests. Während der Tests können "X" in allen Designs auftreten und aus einer Vielzahl von Quellen stammen. Dazu zählen Nicht-Scan-Zellen im Design, die während des Tests nicht überwacht werden können, Embedded-Speicher, der während des Tests nicht initialisiert wird, nicht verbundene Analoglogik, die während des Scan-Tests vergessen wurde, falsche und Multi-Cycle-Pfade sowie viele andere Quellen. Wenn sie nicht richtig gehandhabt werden, können X-States die Effektivität der Kompression auf dem Chip erheblich beeinflussen.

Es gibt mehrere traditionelle Ansätze, X-States bei der Embedded-Kompression zu handhaben, und jeder hat seine eigenen Probleme.

#### 1. "X" ignorieren

Das Ignorieren von "X" beeinflusst die Testabdeckung, das heißt, die Qualität des endgültigen Tests. "X" können echte Fehlereffekte maskieren. Deshalb sind sie während des Fertigungsprozesses unauffindbar. Da das endgültige Ziel der Erhalt oder die Verbesserung der Testqualität ist, sollte diese nicht der Kompression geopfert werden.

## 2. Eliminieren während des Designs

Das Eliminieren von "X" während des Designs macht Designteams zusätzliche Arbeit und erfordert weitere Logik, um alle X-States zu isolieren, die während des Tests auftreten können. Diese Bemühungen verkomplizieren den Designprozess und beeinflussen die Markteinführungszeit.

3. Erzeugen von Top-up-Mustern, welche die Kompressionsschaltung überbrücken Dieser Ansatz bearbeitet "X", indem er zusätzliche unkomprimierte Muster erzeugt, um die Abdeckung (Testqualität) wieder zu erlangen. Die Anzahl der erforderlichen Top-up-Muster kann jedoch ganz erheblich sein und den Umfang der Testdaten und die Testzeit ziemlich erhöhen.

## Xpress – Eine Lösung für das X-State-Problem

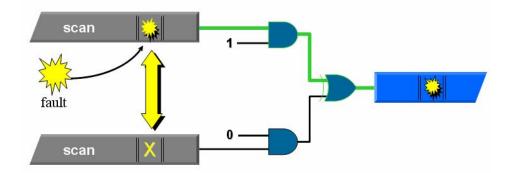

Mentor Graphics' Lösung für das X-State-Problem beinhaltet in der Kompressionsschaltung eine patentierte Technologie, die alle "X" in der Testresonanz selektiv maskiert. Damit stellt sie sicher, dass ein X-State niemals die Testabdeckung oder Testqualität beeinflusst.

Bild 4. Mentors patentiertes X-Handling gewährleistet, dass "X" die Testabdeckung oder Testqualität nicht beeinflussen

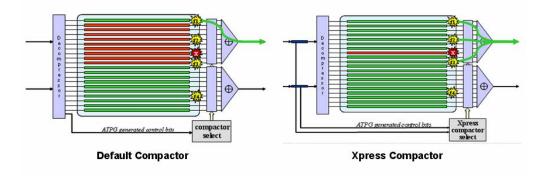

TestKompress Xpress hebt die X-Handling-Technologie auf die nächste Ebene. Der Xpress-Compactor bietet eine effizientere Methode, um "X" zu handhaben. Dazu kombiniert er eine hoch entwickelte Schaltung zur Auswahl der Embedded-Testdaten mit einem fortschrittlichen Softwaresteuerungsalgorithmus. Da die Xpress-Technologie die "X" wesentlich effizienter maskiert, können die Tests kleiner und höher komprimiert sein.

Bild 5. TestKompress Xpress verfügt über neue Auswahl- und Softwaresteuerungsfunktionen zur effizienteren Handhabung von "X". Xpress erlaubt es jedem Muster bei vorhandenen "X", mehr Scan-Chains zu überwachen und dadurch die Musteranzahl zu minimieren und den effektiven Kompressionsgrad zu maximieren.

Zusätzlich zur verbesserten Auswahl und Kontrolle des X-Handlings, enthält Xpress auch neue Softwarekompressionsfunktionen, die die Effektivität der Kompressionsgrade weiter erhöhen, selbst in Designs ohne viele "X". TestKompress Xpress bietet den Anwendern nun Testkompressionsgrade von mehr als dem 100-Fachen.

| Customer Benchmark | Default<br>Compression | Xpress<br>Compression |

|--------------------|------------------------|-----------------------|

| Design A           | 23X                    | 119X                  |

| Design B           | 38X                    | 133X                  |

| Design C           | 62 X                   | 97X                   |

Bild 6. Verbesserungen der effektiven Kompressionsgrade mit TestKompress Xpress.

Die patentierte Xpress-Technologie basiert auf der bestehenden TestKompress-Architektur und deren Fähigkeiten. Aus Anwendersicht gibt es keine Änderung im Design- oder Testablauf. Da während der ATPG alle X-Handling-Controls innerhalb des Testmusters programmiert sind, bleibt der Ablauf der Mustererzeugung ebenfalls unverändert.

#### **Fazit**

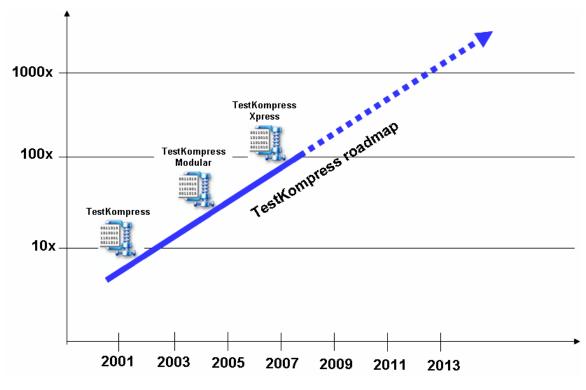

Der Qualitätserhalt ist in der Nanometer-Ära der treibende Faktor hinter der Einführung von Testkompressionstechnologien. Großserienprodukte werden an jedem neuen Technologieknoten weiterhin steigende Kompressionsgrade benötigen, um die Testkosten zu managen. Gleichzeitig fügen sie volle Anzahl von Tests hinzu, die erforderlich sind, um niedrige DPM-Level zu gewährleisten. Für Halbleiterunternehmen wird eine Technologie immer wichtiger, die hohe Testkompression bietet, ohne die Testabdeckung/Testqualität zu beeinflussen und dem funktionalen Design oder dem Ablauf der Testentwicklung zusätzliche Komplexität oder Bedingungen hinzuzufügen. Im Jahr 2001 hat Mentor Graphics TestKompress vorgestellt, das erst kommerziell verfügbare Produkt zur Embedded-Kompression. Seitdem wurden mehrere wesentliche Erweiterungen hinzugefügt, die den effektiven Kompressionsgrad vom 10-Fachen in 2001 auf das über 100-Fache mit TestKompress Xpress steigern.

**Bild 7. Mentors Roadmap zur Test-Kompression**

Mentors Roadmap zur Testkompression zeigt, dass dank neuer Technologien wie dem gerade in Entwicklung befindlichen Compression-Overdrive innerhalb der nächsten paar Jahre Kompressionsfaktoren um das 1000-Fache zur Verfügung stehen werden.

Mentor Graphics und TestKompress sind eingetragene Warenzeichen der Mentor Graphics Corporation. Alle übrigen Unternehmens- oder Produktnamen sind eingetragene Warenzeichen oder Warenzeichen ihrer jeweiligen Besitzer.