| Mentor Graphics liefert nächste Generation der funktionalen Verifikation |

| Tools, Methodologien und Partner verbessern Produktivität und Effizienz der Verifikation |

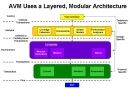

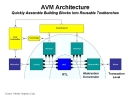

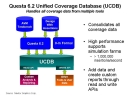

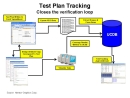

| WILSONVILLE, Oregon/USA, 08. Mai 2006 - Mentor Graphics Corporation kündigt seine umfangreiche Questa-Verifikationslösung der nächsten Generation an. Diese kombiniert Tools, Methodologien sowie Industriepartner und bietet Designern von heute einen neuen Level an Produktivität und Effizienz in der Verifikation. Die Ankündigung beinhaltet die neue funktionale Verifikationsplattform Questa 6.2, die industrieweit erste standardbasierte Open-Source-Advanced-Verification-Methodology (AVM) und das Questa-Vanguard-Program (QVP), ein Partnerprogramm mit über 25 Unternehmen, die anderen Unternehmen dabei helfen, effektivere Verifikations-Flows aufzubauen. Tools an sich lösen keine Probleme, sagte Robert Hum, Vice President und General Manager von Mentor Graphics Design Verification and Test Division. Erforderlich sind Standards, Methodologien und eine industrielle Infrastruktur, die Anwender nutzen und deren neue Fähigkeiten sie schnell einsetzen können. Die neue Questa-Lösung adressiert all diese Anforderungen und ist einmalig positioniert, um die Adaption neuer, von Designern benötigter Flows zu beschleunigen. Neue Verifikationstechniken erfordern eine Methodologie Die neue Advanced-Verification-Methodology (AVM) ist die erste echte System-Level-zu-RTL-Verifikations-Methodologie. Sie integriert fortschrittliche Verifikationstechniken wie Constrained-Random-Stimulus, funktionale Coverage und Assertions in ein einzelnes Transaction-Level-Modeling(TLM)-basiertes Framework, das sowohl in SystemC als auch in SystemVerilog implementiert ist. Von Anfang an entwickelt, um die Vorteile der neuen Verifikationsmöglichkeiten in SystemC und SystemVerilog nutzen zu können, bietet das AVM einen objektorientierten Codierungsstil, mit dessen Hilfe sich der Testbench-Code reduzieren lässt, sowie eine modulare Architektur, die Wiederverwendbarkeit ermöglicht. Die AVM besteht aus dem AVM-Kochbuch, einem Handbuch zum schnellen Start, dem industrieweit ersten Quellcode für Base-Class-Bibliotheken, Dienstprogrammen und Implementierungsbeispielen, die in SystemC und SystemVerilog geschrieben sind. Der AVM-Code wird zusammen mit der AVM-Dokumentation unter einer Apache-2.0-Open-Source-Lizenz bereitgestellt. Derzeitige und zukünftige Designs, die immer größer und komplexer werden, erfordern innovative Lösungen. Die Verifikation bleibt der größte Engpass im Designzyklus und erfordert einen Umstieg auf neue Methodologien und Tools zur Überwindung dieses Flaschenhalses, erklärte Predrag Markovic, CEO von HDL Design House. Questa bietet eine vollständige standardbasierte Single-Kernel-Verifikationsumgebung, welche die Produktivität der Verifikation erhöht und den Wechsel auf neue Methodologien wie Coverage-gesteuert und Assertions-basierte Verifikation sowie Transaction-Level-Modeling ermöglicht. Questa beinhaltet den SystemVerilog-Standard und gewährleistet deshalb zukünftig Wiederverwendbarkeit und Designportabilität. Questa 6.2 und AVM bieten Designern modernste Verifikationsmöglichkeiten Die Questa-6.2-Plattform ist eine mehrsprachige Verifikationslösung für Simulation, Assertions, Coverage und Testbench-Automatisierung. Questa 6.2 unterstützt alle wesentlichen Komponenten des AVM: die objektorientierten und Constrained-Random-Fähigkeiten von SystemVerilog und SystemC, die Standardfunktionalität von OSCI-TLM und die funktionale Coverage von SystemVerilog und PSL. Keine andere derzeit verfügbare Lösung bietet diese breite Palette an fortschrittlichen Fähigkeiten in Standardsprachen. Questa bietet neue, einmalige Coverage-Möglichkeiten zur Erhöhung der Verifikationseffizienz Zusammen mit dem Leistungszuwachs und den neuen Debugging-Fähigkeit enthält Questa 6.2 auch die erste Unified-Coverage-Database (UCDB). Die UCDB eliminiert die Komplexität beim Erfassen und Managen von Coverage-Daten und vereinigt alle von der Questa-6.2-Plattform generierten Verifikation-Coverage-Daten (inklusive weiterer Verifikationstechnologien von Mentor wie 0-In®- und Seamless-Tools). Mit der konsolidierten Coverage-Analyse können Designer die Effizienz der Verifikation erhöhen, denn sie können ungenutzte Simulationszyklen identifizieren und eliminieren, freiliegende Flächen im Design schnell entdecken und die Verifikationsschleife schließen, indem sie die Coverage-Ergebnisse direkt mit den original Testplan zurück verbinden. Zahlreiche Industriepartner vervollständigen das Bild Ohne adäquate Infrastruktur in der Industrie kann keine neue Technologie oder Methodologie erfolgreich sein. Mit dem QVP hat sich Mentor mit führenden Unternehmen im Bereich Schulung, Consulting und Verifikations-IP zusammengeschlossen, um die Adaption neuer Verifikationssprachen und technologien zu vereinfachen und zu beschleunigen (siehe auch die Pressemitteilung Questa Vanguard Program vom 08. Mai 2006). Jeder dieser Anbieter arbeitet sehr eng mit Mentor zusammen, um zu gewährleisten, dass seine Produkte die Questa-Plattform und die AVM unterstützen. Questas führende Unterstützung für die Verifikation mit SystemVerilog, ist einer der Hauptgründe warum wir diese besondere Lösung gewählt haben, kommentierte Tim Holden, Director EDA Relations bei ARM Ltd. Wir sind in der Lage, mit Hilfe von Questas nativer SystemVerilog-Implementierung eine sehr hoch entwickelte Coverage-gesteuerte Constrained-Random-Verifikationsumgebung zu entwickeln. Dies verkürzt unseren Entwicklungszyklus im Vergleich zu vorherigen Projekten erheblich. Questa nutzt die Vorteile von SystemVerilog, indem es eine Single-Kernel-Verifikationslösung zur Verfügung stellt, die im Gegensatz zu mehrsprachigen Multi-Tool-Lösungen Performance- und Debugging-Vorteile bietet. Verfügbarkeit Die Verifikationsplattform Questa 6.2 ist ab dem 2. Quartal 2006 erhältlich und beinhaltet auch den Zugang zum Advanced-Verification-Methodology-Portal. Die AVM ist kostenlos als Standard-Open-Source-Lizenz ab dem 2. Quartal 2006 verfügbar. Weitere Produktinformationen gibt es unter http://www.mentor.com/questa |

| Über Mentor Graphics Corporation Mentor Graphics Corporation (Nasdaq: MENT) gehört zu den weltweit führenden Unternehmen, die Software- und Hardwarelösungen für die Entwicklung elektronischer Schaltungen anbieten. Zu Mentors Portfolio gehören Produkte, Beratungs- und Supportdienstleistungen, auf die die weltweit erfolgreichsten Elektronik- und Halbleiterhersteller vertrauen und dies mit der Verleihung zahlreicher Auszeichnungen an Mentor zum Ausdruck gebracht haben. Das 1981 gegründete Unternehmen erzielte in den zurückliegenden zwölf Monaten einen Gesamtumsatz von über 700 Mio. US-Dollar und beschäftigt weltweit ca. 4.000 Mitarbeiter. Der Hauptsitz von Mentor Corporate befindet sich den USA, 8005 S.W. Boeckman Road, Wilsonville, Oregon 97070-7777; Die Adresse der Niederlassung im Silicon Valley lautet: 1001 Ridder Park Drive, San Jose, Kalifornien 95131-2314. Weitere Informationen unter: http://www.mentor.com |

| Presse Informationen online: | 6366 |

| Presse Informationen | | | Newsletter | | | Suche | | | Agentur | | | English |